#### UNIVERSITY OF CALIFORNIA SAN DIEGO

#### Next Generation Cloud-FPGA Side-Channels

A thesis submitted in partial satisfaction of the requirements for the degree Master of Science

in

**Computer Science**

by

Colin Drewes

Committee in charge:

Professor Ryan Kastner, Chair Professor Dean Tullsen Professor Deian Stefan

2022

Copyright Colin Drewes, 2022 All rights reserved. The thesis of Colin Drewes is approved, and it is acceptable in quality and form for publication on microfilm and electronically.

University of California San Diego

2022

### DEDICATION

To my loving family: Mom, Dad, Claire, Richard, Heidi, Jim, Conrad, Conor, Tucker, Boomer, and Aspen.

### EPIGRAPH

Highly organized research is guaranteed to produce nothing new. —Frank Herbert, Dune

### TABLE OF CONTENTS

| Thesis Appro    | oval Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Dedication .    | iv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Epigraph        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table of Con    | tents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| List of Figure  | esviii                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| List of Table   | s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Acknowledg      | ements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Abstract of the | ne Thesis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Chapter 1       | FPGAs in the Cloud                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Chapter 2       | FPGA Fabric Sensors42.1 Ring Oscillators52.2 Tunable Dual-Polarity TDC52.2.1 Pulse Generator72.2.2 Programmable Clock Generators72.2.3 Delay Line and Capture Registers82.2.4 $\theta$ and $\phi$ Tuning102.2.5 Propagation Metric102.3 Acknowledgements11                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Chapter 3       | Power Side-channels       13         3.1       Power Distribution Network       13         3.2       Threat Model       14         3.3       Experimental Setup       14         3.3       Experimental Setup       16         3.4       Applications       16         3.5       θ Tuning and Metric Selection       18         3.5.1       First Index       20         3.5.2       Last Index       20         3.5.3       Binary Hamming Distance       21         3.5.4       Analysis       21         3.6 $\phi$ Tuning and Background Subtraction       22         3.6.1       AWS Sensor Only       23         3.6.2       PYNQ-Z2 Sensor Only       24         3.6.3       PYNQ-Z2 PicoRV AES       25 |

|              |       | 3.6.4 Effects of Tuning on Classification | 5 |

|--------------|-------|-------------------------------------------|---|

|              | 3.7   | Effects of Tuning on CPA                  | 3 |

|              | 3.8   | Related Work                              | 5 |

|              | 3.9   | Acknowledgements                          | 1 |

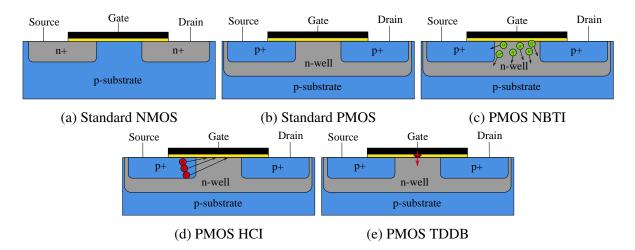

| Chapter 4    | Trans | sistor Side-Channels                      | ) |

|              | 4.1   | TDCs as a Timing Instrument               | ) |

|              | 4.2   | Transistor Degradation                    | ) |

|              |       | 4.2.1 Hot Carrier Injection               | 2 |

|              |       | 4.2.2 Time-Dependent Dielectric Breakdown | 2 |

|              |       | 4.2.3 Bias Temperature Instability        | ; |

|              | 4.3   | NBTI as a Side-Channel44                  | ł |

|              | 4.4   | Threat Model                              | 5 |

|              | 4.5   | Experimental Setup                        | 1 |

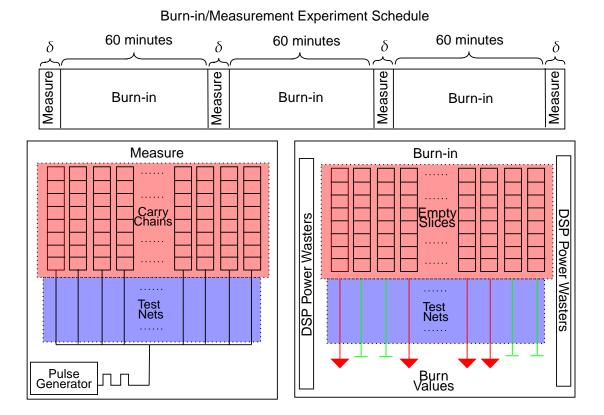

|              |       | 4.5.1 Designs                             | 3 |

|              |       | 4.5.2 Experiment Phases                   | L |

|              | 4.6   | Results                                   | ; |

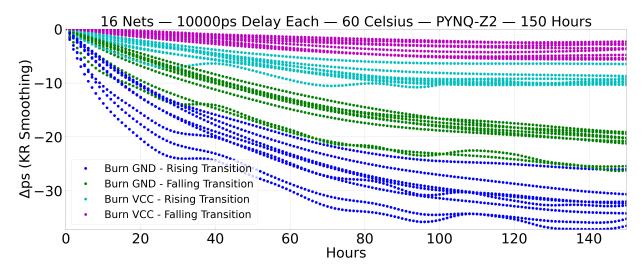

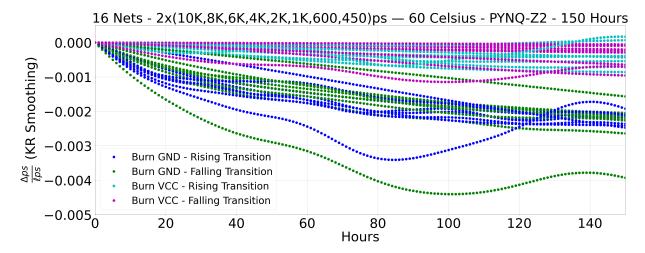

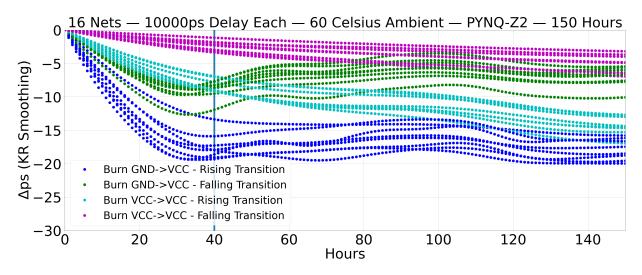

|              |       | 4.6.1 PYNQ-Z2                             | 3 |

|              |       | 4.6.2 ZCU102                              | ) |

|              |       | 4.6.3 AWS F1                              | 3 |

|              | 4.7   | Leveraging Elasticity as an Attack        | 1 |

|              | 4.8   | Related Work                              | 3 |

|              | 4.9   | Acknowledgements                          | ) |

| Chapter 5    | Conc  | clusion                                   | L |

| Bibliography |       |                                           | 3 |

### LIST OF FIGURES

| Figure 2.1:<br>Figure 2.2: | Architecture of the Tunable Dual-Polarity Time-To-Digital Converter $\phi$ and $\theta$ define the relationship between the launch, capture and target clocks                               | 6        |

|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1 iguite 2.2.              | in our Tunable Dual-Polarity Time-to-Digital Converter.                                                                                                                                     | 9        |

| Figure 3.1:                | Remote TDC Threat Model                                                                                                                                                                     | 14       |

| Figure 3.2:                | Comparison of the three propagation metrics described in Section 2.2 and two transition polarities as $\theta$ is increased from 0 ps                                                       | 19       |

| Figure 3.3:                | Measuring sensor output as $\phi$ is swept from 0 to $4\pi$ on the AWS Sensor Only Design. Background noise is consistent across multiple sweeps of $\phi$                                  | 24       |

| Figure 3.4:                | Measuring sensor output as $\phi$ is swept from 0 to $4\pi$ on the PYNQ-Z2 Sensor Only Design. Background noise is consistent across multiple sweeps of $\phi$ .                            | 25       |

| Figure 3.5:                | Measuring sensor output as $\phi$ is swept from 0 to $4\pi$ on PYNQ-Z2 PicoRV AES design.                                                                                                   | 26       |

| Figure 3.6:                | Our Tunable Dual-Polarity TDC is employed in a 13-way classification task where an attacker extracts the type of co-located computation.                                                    | 27       |

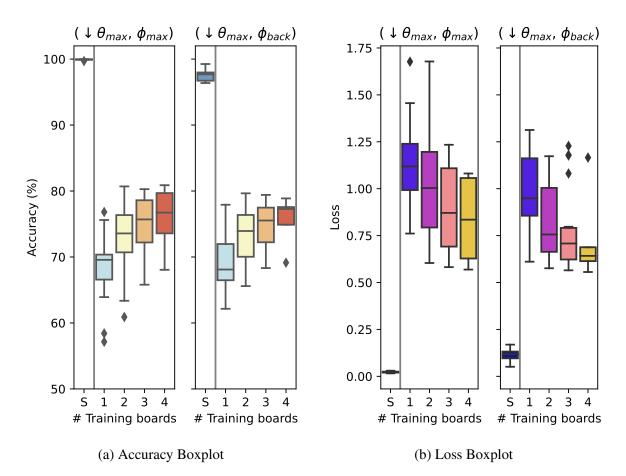

| Figure 3.7:                | Training on an increasing number of boards with background subtraction $(\downarrow \theta_{max}, \phi_{back})$ and without $(\downarrow \theta_{max}, \phi_{max})$ .                       | 32       |

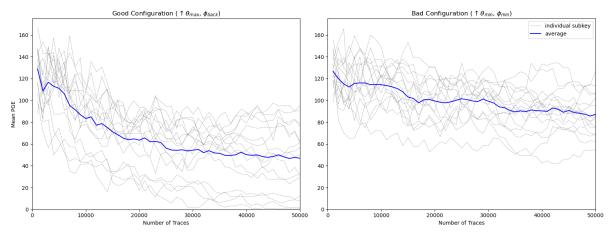

| Figure 3.8:                | Evaluating performance of the CPA attack for configurations obtained via the $(\uparrow \theta_{max}, \phi_{back})$ and $(\uparrow \theta_{min}, \phi_{min})$ tuning methods.               | 33       |

| Figure 4.1:                | Simplified cross sectional view of NMOS and PMOS transistors and degra-<br>dation mechanisms.                                                                                               | 41       |

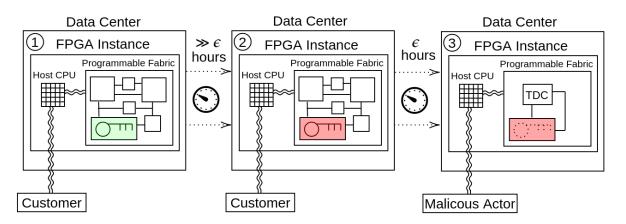

| Figure 4.2:<br>Figure 4.3: | The proposed cloud-FPGA user-to-user leakage threat model This figure presents 3 hours of the <i>Burn-in/Measurement</i> phase of our experiment, and a high level view of the designs used | 45<br>48 |

| Figure 4.4:                | 16 nets of an estimated 10000ps delay are instantiated on the PYNQ-Z2 and biased with an alternating pattern of VCC and GND.                                                                | 55       |

| Figure 4.5:                | 16 nets of varying length are instantiated on the PYNQ-Z2 and biased with an alternating pattern of VCC and GND                                                                             | 56       |

| Figure 4.6:                | 16 nets of an estimated 10000ps delay are instantiated on the PYNQ-Z2 and biased with an alternating pattern of VCC and GND.                                                                | 58       |

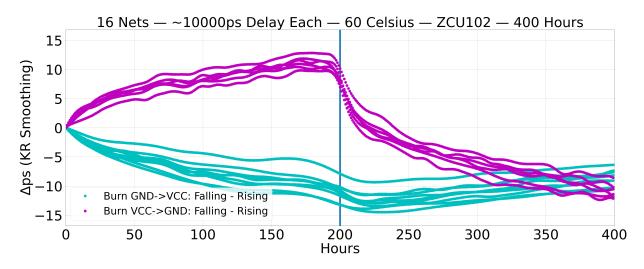

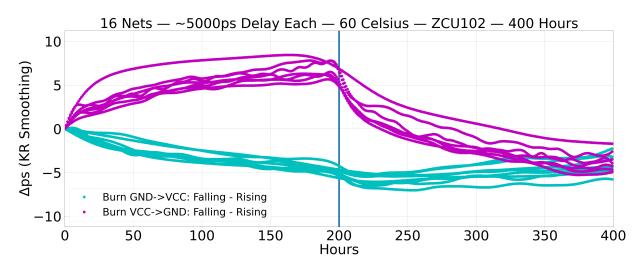

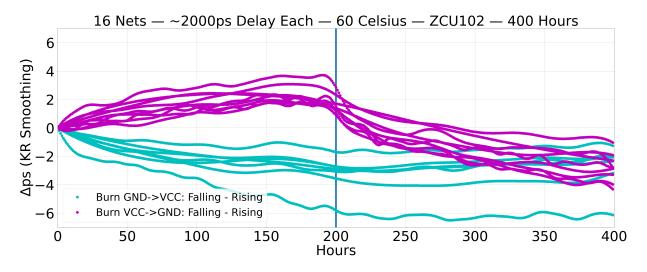

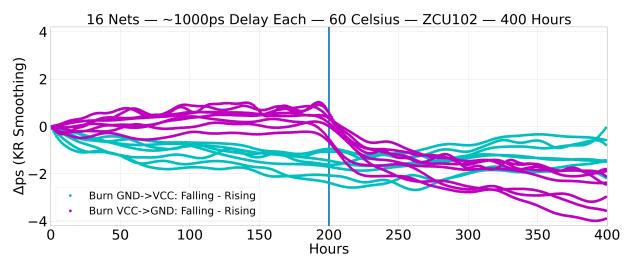

| Figure 4.7:                | 16 nets of 10000ps each are initialized with a random burn value (GND or VCC) on the ZCU102.                                                                                                | 60       |

| Figure 4.8:                | 16 nets of 5000ps each are initialized with a random burn value (GND or VCC) on the ZCU102.                                                                                                 | 61       |

| Figure 4.9:                | 16 nets of 2000ps each are initialized with a random burn value (GND or VCC) on the ZCU102.                                                                                                 | 61       |

| Figure 4.10:               | 16 nets of 1000ps each are initialized with a random burn value (GND or VCC) on the ZCU102.                                                                                                 | 62       |

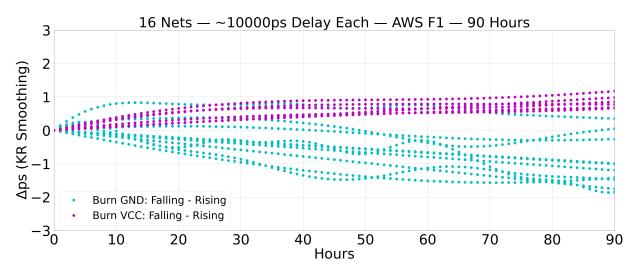

| Figure 4.11:               | 16 nets of 10000ps each are initialized with a random burn value (GND or VCC) on AWS F1                                                                                                     | 64       |

| Figure 4.12: | 16 nets of 5000ps each are initialized with a random burn value (GND or       |    |

|--------------|-------------------------------------------------------------------------------|----|

|              | VCC) on AWS F1.                                                               | 65 |

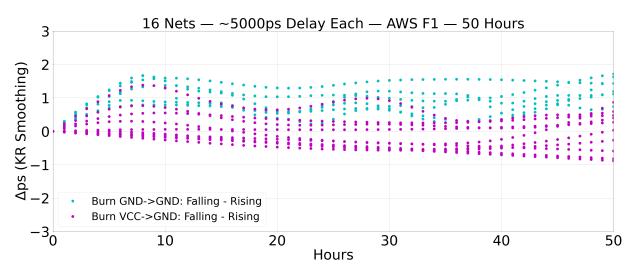

| Figure 4.13: | 16 nets of 10000ps each are initialized with a random burn value (GND or      |    |

|              | VCC) on AWS F1 and allowed to sit for 96 hours. We then study their recovery. | 66 |

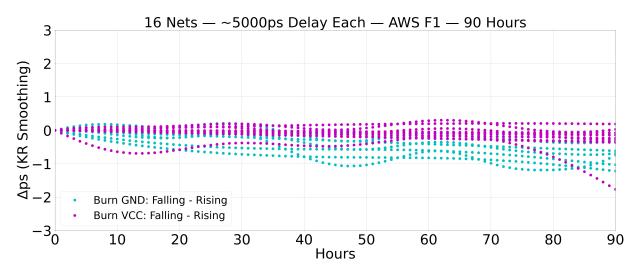

| Figure 4.14: | 16 nets of 5000ps each are initialized with a random burn value (GND or       |    |

|              | VCC) on AWS F1 and allowed to sit for 96 hours. We then study their recovery. | 67 |

#### LIST OF TABLES

| Table 3.1: | Average accuracy and loss across configurations. | 30 |

|------------|--------------------------------------------------|----|

| Table 3.2: | Evaluation of CPA attack performance             | 35 |

#### ACKNOWLEDGEMENTS

I owe a special thanks to Professor Ryan Kastner, of the University of California, San Diego, for his support of this work both financially and intellectually, as well as me as a researcher.

The work contained in this thesis was only possible with the support of Dr. Dustin Richmond, of the University of Washington, for the early engineering work that this paper builds on, helping draft portions of this work, and guiding me with engineering, writing, and academic questions.

This project also benefited greatly from the advice, encouragement, and wealth of knowledge from Bill Hunter, of the Georgia Tech Research Institute. This thesis also explored ideas originally presented by Christopher McCarty, also of the Georgia Tech Research Institute.

This thesis builds on predecessor work I completed with Mustafa Gobulukoglu of the University of California, San Diego, which resulted in a Design and Automation Conference publication [GDH<sup>+</sup>21].

Portions of Chapter 3 of this thesis were completed with the assistance of PhD students Olivia Weng and Keegan Ryan, at the University of California, San Diego. This section also benefited from the work of Winnie Wang and Steven Harris.

Chapter 4 is due in a large part to ideas and early work of Dr. Dustin Richmond and Professor David Kohlbrenner, of the University of Washington.

Finally, a great thanks to my committee chair Professor Ryan Kastner and committee members Professor Deian Stefan and Professor Dean Tullsen.

xi

#### ABSTRACT OF THE THESIS

#### **Next Generation Cloud-FPGA Side-Channels**

by

Colin Drewes

Master of Science in Computer Science

University of California San Diego, 2022

Professor Ryan Kastner, Chair

Cloud-FPGAs are an attractive alternative compute option for accelerating consumer computation without the need to purchase a multi-thousand dollar device. The greatest strength of these devices, their reconfigurability, comes at a cost in terms of opening new attack vectors.

We first consider an attractive cloud-FPGA model that has garnered great commercial and academic interest for reducing costs and maximizing utilization: the virtualization of cloud-FPGA resources, called multi-tenancy. However, side-channel leakage poses a major security threat in multi-tenant FPGA environments. A tenant can instantiate a signal timing sensor that measures minute changes in the power distribution network and infer information about co-tenant computation. This work presents the Tunable Dual-Polarity Time-to-Digital Converter (TDC)—a signal timing sensor with three dynamically tunable parameters: the sample duration, clock phase, and frequency.

Returning to the existing cloud-FPGA model, we present, to the best of our knowledge, the first remote measurement of bias temperature instability, a type of transistor degradation, on a commercial cloud-FPGA platform. We re-purpose the same on-fabric TDC testing mechanism as before. A study is provided demonstrating this bias effect within the FPGA routing, characterizing its relationship to the number of transistors in the underlying tested element, and exploring its elastic nature, on three different architectures: PYNQ-Z2, ZCU102, AWS F1. We present a novel attack vector that leverages this effect in cloud-FGPAs, where a malicious user can extract secrets from previous user's computation.

# Chapter 1

# **FPGAs in the Cloud**

Cloud providers have begun offering FPGAs as a rent-able service. Their versatility makes them ideal compute off-load engines for neural networks [FOP<sup>+</sup>18], genome sequencing [CCF<sup>+</sup>16], secure database transactions [AEJ<sup>+</sup>15], networking [PCC<sup>+</sup>14], and homomorphic encryption [PNPM15]. These applications often place strict security requirements on their computation to be enforced by the cloud-FPGA provider.

As cloud providers deploy FPGAs in data centers, it is becoming increasingly clear that current schemes leave large portions of the fabric under-utilized. Virtualization, or the abstraction of physical hardware resources, has been proposed to maximize utilization by supporting multiple concurrent users [ZL20]. It has the potential to reduce costs for host and consumer, making it an attractive option for cloud service providers.

Virtualization of shared resources introduces a new class of security attacks that leverage the shared power distribution networks in FPGA systems. These attacks implement some variant of a signal timing sensor within the programmable logic of the device. These sensors can measure minute voltage changes in the power distribution network that expose information about other users within the same chip. The use of such sensors as a covert channel [ZS18, SGMT18b], a side-channel to extract cryptographic keys of co-located encryption cores [ZS18, SGMT18b], or recognizing co-tenant IP cores [GDH<sup>+</sup>21] is well demonstrated. Although this architecture remains unrealized, we will examine in Chapter 3 these security vulnerabilities in more detail.

We return, in Chapter 4, to the existing cloud-FPGA model where users are allocated an entire device for as long as their computation takes. We will utilize an identical signal timing sensor as with the previous attack, but to instead measure minute changes in circuit-level timing behavior due to transistor degradation that leak information of a previous user's computation. Our findings demonstrate that due to transistor reliability issues, sensitive information can be leaked across successive users of the same FPGA device, and recovered with our proposed sensor design.

In this paper, for both these vulnerabilities, we examine the design of a sub-class of these signal timing sensors, called Time-to-Digital Converters (TDC), that measure the propagation delay of a signal. TDCs can be built from a linear array of logic elements with uniform delay. The propagation speed of the delay elements is a function of the power distribution network voltage, but also the speed of the signal through its path to reach the linear array of logic elements. Voltage fluctuations over time as well as changes in the speed of a signal through some circuit element over time can be measured with consecutive output captures.

We present the design of the *Tunable Dual-Polarity TDC* which is novel in its ability to dynamically tune its sensing parameters including transition polarity, sample window, duration, phase, and frequency. We examine in our power side-channel attack on virtualized FPGAs how these features improve the sensor's ability to capture information about a co-tenant and improve cross-board generalization. As a tangible measure of the importance of our sensor's features, we examine how the tuning phase relationship between the Tunable Dual-Polarity TDC and the co-tenant clock influences the ability to capture side-channel leakage. These tactics are employed in a 13-way classification task where an attacker is attempting to learn about the architecture and algorithm running in a multi-tenant environment in order to perform a side-channel attack.

Our experiments demonstrate that transition polarity, metric selection, phase and duration

2

tuning, and background subtraction, are important factors in maximizing channel information and a well tuned sensor can improve classification accuracy by  $2.5 \times$ . After successfully identifying an AES computation with our classification network, we demonstrate that proper sensor calibrations increases the frequency with which all correct subkey values are ranked as most likely by  $2 \times$  in a Correlation Power Analysis attack.

In our transistor degradation side-channel attack, we begin with a study of the relationship between low level transistor degradation and high level circuit behavior with the use of our Tunable Dual-Polarity TDC. We then establish a connection between these low level effects and aspects of previous computation, laying the ground work for our data recovery attack. Finally, we demonstrate how an attacker can recover logical values held within the circuit of a previous user's cloud-FPGA design, with a particular focus on the importance of our Tunable Dual-Polarity TDC's ability to capture both transition polarities. This analysis is performed in local environments, on a PYNQ-Z2 and ZCU102, as well as AWS's real could-FPGA environment.

# Chapter 2

# **FPGA Fabric Sensors**

The primary goal of this work is to demonstrate *remote* attacks on cloud FPGAs, and consequently, it is necessary to implement our sensors within the programmable logic of the FPGA itself. We focus on two side-channels in this work, power and transistor degradation. The ability to measure power on a shared FPGA, as presented in Section 3.1, allows a user to extrapolate information about other FPGA co-tenant users based on the profile of their power consumption. The ability to measure transistor degradation has the potential to leak secrets across subsequent users of an FPGA and expose proprietary intellectual property in designs—presented in Section 4.2.

There exist two broad classes of sensors which can be implemented within the FPGA fabric that simultaneously solve both these problems. The first we consider in Section 2.1 is the canonical choice, ring oscillators. While these can be used to both measure on-chip power and on-chip transistor degradation, they are limited by the ease of their detection through bitstream analysis tools. Though, their simplicity for solving both these tasks warrants their mention. For the rest of this paper, however, we turn to TDCs, which also can measure on-chip power and transistor degradation, yet can remain incognito in FPGA designs.

## 2.1 Ring Oscillators

Ring Oscillators (ROs) are a primitive type of signal timing sensor [BLB97, ZH12]. ROs are metastable circuits implemented in the FPGA fabric that alternate between 0 and 1. This can be constructed through the use of a combinatorial loop with a single inverter, resulting in rapid oscillation. Every transition causes an attached counter to increment, allowing the frequency of the oscillation to be derived. The oscillation frequency is a function of the speed of the transition through the combinatorial loop. This speed is dependent on the voltage of the FPGA power grid as well as the transistor switching speed. An attacker can track voltage fluctuations by measuring the changes in an oscillator-driven counter value over time, or alternatively as we will see, recover leaked information based on transistor speed.

In order to accomplish the required free-running oscillation of these sensors, the design must rely on the introduction of a timing violation, and in many cases, act as a potentially damaging circuit for the part. While these circuits can still be implemented in FPGA designs, it often requires explicitly ignoring certain Design Rule Checks (DRC). As a result, these sensors cannot be deployed on cloud-FPGA instances as we intend. Further attempts to disguise these sensors are thwarted by the bitstream analysis tools presented in [KGT19].

On the contrary, TDC are stealthier because they do not introduce DRC violations nor do they necessitate timing violations. Their structure resembles that of a carry adder which is ubiquitous in FPGA designs.

## **2.2 Tunable Dual-Polarity TDC**

Our Tunable Dual-Polarity Time-to-Digital Converter (TDC) has four key features: 1) it captures both rising and falling transition polarities (Dual-Edge); 2) it provides real-time adjustment of the sample window duration; 3) it provides real-time phase adjustment of the sample clock relative to the target computation; and 4) it provides real-time frequency adjustment

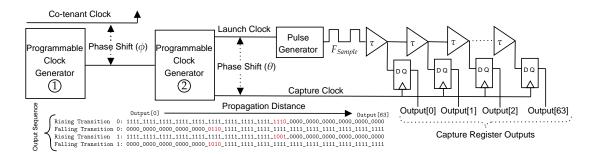

**Figure 2.1**: Architecture of the Tunable Dual-Polarity Time-To-Digital Converter. A pulse generator produces positive and negative pulse edges that cause falling and rising transitions to propagate through a linear array of delay line elements. The transitions are captured in mid-flight by output capture registers in the capture clock domain. Voltage fluctuations on the power distribution network of the FPGA affect the propagation speed of the delay line and cause variations in a metastable region around the transition point (highlighted in red).

of the sample clock. We will leverage these features to tune the sensor to the voltage fluctuations of an FPGA power distribution network (PDN) caused by a target core.

Figure 2.1 demonstrates the architecture of the Tunable Dual-Polarity TDC. The core of the sensor is a pulse generator that induces rising and falling transitions through a delay line at a configurable frequency  $F_{sample}$ . A single pulse contains both a positive  $(0 \rightarrow 1)$  and a negative  $(1 \rightarrow 0)$  pulse edge. Positive and negative pulse edges are issued sequentially by the pulse generator in the Launch Clock domain. Pulse edges cause falling and rising transitions to propagate through a linear array of delay line elements to the Output capture register, which is controlled by the Capture Clock.  $\theta$  is the phase difference between the Launch Clock and the Capture Clock; it is the time between the launch of a pulse and the subsequent capture of the transition in the output registers. When  $\theta$  is set correctly, a transition will be propagating through the delay line when the output registers are clocked and record a metastable transition region. The distance that transition propagates is called the propagation distance.

An example output sequence from two consecutive pulses is shown at the bottom of Figure 2.1. Each pulse causes a falling and rising transition to be captured at the output. Rising Transition 0 shows that the  $0 \rightarrow 1$  transition reached Output [38]<sup>1</sup>. Falling Transition 0 shows

<sup>&</sup>lt;sup>1</sup>Figure 2.1 lists the output sequences from least significant bit (Output [0]) on the left to most significant bit

that the  $1 \rightarrow 0$  propagated to somewhere between Output[21] and Output[23], with some metastability between the two points. In the next pulse, Rising Transition 1 propagates differently; the  $0 \rightarrow 1$  transition propagates to between Output[36] and Output[39]. Similarly, Falling Transition 1 propagates to between Output[20] and Output[23]. These changes can reflect voltage fluctuations in the PDN, which affect the propagation speed of the delay line, and the presence of metastability. The variations provide potential information about the operation of the FPGA including the computation by other co-tenants.

The sampling frequency is dictated by the length of the delay line and the speed of the underlying FPGA logic. If a higher effective sampling frequency is needed, multiple launch/capture clock pairs with a known phase offset can be generated by the clock generator as is done in related work [SZY<sup>+</sup>20, CJ20, WKL16]. The remainder of this section describes a sensor with a single delay line.

#### 2.2.1 Pulse Generator

The pulse generator produces positive  $(0 \rightarrow 1)$  and negative  $(1 \rightarrow 0)$  pulse edges that cause falling and rising transitions, respectively, in the delay line. Each pulse produces a rising and a falling transition on the capture registers, and a series of outputs is a trace. The pulse generator has two run-time configurable parameters: the sampling frequency  $F_{sample}$ , which is an integer fraction of the launch clock frequency, and the number of pulses. Figure 2.1 demonstrates a trace length of two, which produces two rising transitions and two falling transitions. We demonstrate that both transitions contain useful information in Section 3.2.

#### 2.2.2 Programmable Clock Generators

The Tunable Dual-Polarity TDC has two programmable clock generators implemented using a Xilinx Mixed-Mode Clock Manager (MMCM). The first MMCM, ① in Figure 2.1, (Output[63]) on the right. controls the input clock to the Tunable Dual-Polarity TDC and the phase relationship  $\phi$  between the target clock and the sensor clock. Section 3.6 discusses the importance of tuning  $\phi$  to better capture relevant information about a co-located computation.

A second MMCM (2) in Figure 2.1) generates the launch and capture clocks with a programmable phase offset,  $\theta$ , between them. Changing  $\theta$  modifies the length of time between when an edge is generated by the pulse generator and when the capture clock fires and records the location of the subsequent transition in the output registers. Section 3.5 demonstrates the importance of tuning  $\theta$ .

During compilation the TDC sensor is configured to pass timing checks. The phase relationship  $\phi$  is unconstrained and  $\theta$  is set to  $2\pi$ . This means that the TDC sensor cannot be detected by tools that check for timing violations [KGT19].

#### 2.2.3 Delay Line and Capture Registers

The delay line in Figure 2.1 is a series of combinational logic elements that propagate the rising and falling transitions caused by the pulse generator. The delay elements are constructed from identical digital circuit elements that provide a linear propagation delay,  $\tau$ . The delay elements of a well-designed TDC should be placed and routed with uniform spacing to ensure consistent delay between each element and a regular delay through the entire chain.

The interplay between the number of bits in the delay line and  $\theta$  is also an important TDC

design consideration. The maximum value of  $\theta$  and the sampling frequency is limited by the length of the delay line. A delay line that is too short may not capture all of the PDN variations induced by a target, but a long delay line increases resource consumption. Characterizing how a target computation affects the PDN, and what values of  $\theta$  best measure variations is important for tuning the sensor to provide the most information.

The capture registers shown in Figure 2.1 record the output of each bit of the carry delay line in the capture clock domain. The path from the pulse generator to the high-order-bit of the output meets timing constraints in the FPGA toolchain, and the launch clock and capture clock are configured to be in-phase during compilation. This means that the TDC sensor cannot be detected by tools that check for timing violations [KGT19].

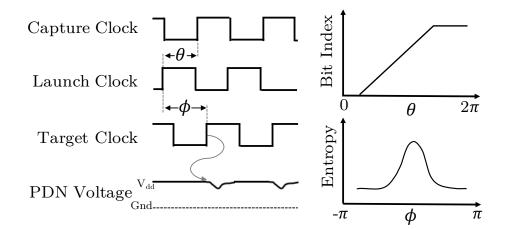

**Figure 2.2**:  $\phi$  and  $\theta$  define the relationship between the launch, capture and target clocks in our Tunable Dual-Polarity Time-to-Digital Converter.  $\theta$  is the known phase relationship between the launch and capture clocks and affects the location of the transition bit index.  $\phi$  is the unknown phase relationship between the launch and target clock. Variations in PDN voltage are caused by power consumption around the positive edge of the target clock. As  $\phi \rightarrow 0$  the variations caused by the target clock will be seen by the TDC sensor and maximize the measured entropy. We use standard deviation as a measure of channel information.

#### **2.2.4** $\theta$ and $\phi$ Tuning

The programmable clock generators allow the Tunable Dual-Polarity TDC to tune its parameters to optimize the information sampled from the PDN. Figure 2.2 defines the relationship between the target clock, the capture clock, and the launch clock using  $\theta$  and  $\phi$ ; the effect of the target computation on  $V_{dd}$ ; and the effect of varying  $\theta$  and  $\phi$  on measured channel information (entropy). The PDN voltage  $V_{dd}$  varies in response to the target computation's rising edge.

$\theta$  is the time between the launch of an edge and the subsequent capture of the transition. The upper right graph in Figure 2.2 demonstrates the effect of varying  $\theta$  from 0 to  $2\pi$ . Increasing  $\theta$  provides more time for the pulse to propagate through the delay line; as  $\theta$  increases, the bit index of the transition increases. Section 3.5 experimentally demonstrates the importance of tuning  $\theta$ .

$\phi$  is phase relationship between the sampling clock and the target computation. The lower right graph in Figure 2.2 demonstrates the effect of varying  $\phi$  from  $-\pi$  to  $\pi$ . Changing  $\phi$  will move the sampling window over the variations in the power distribution network. When the sampling window is positioned over the variations in the power distribution network caused by the target clock, the sensor output will vary between cycles in response to the variations in power consumed by the target. This will cause an increase in the channel information measured at the sensor. The channel is maximized at the point of highest entropy. Our TDC sensor enables  $\phi$  to be tuned to ensure that the sample window is optimized with respect to the target computation. Section 3.6 experimentally demonstrates this effect.

#### 2.2.5 Propagation Metric

When  $\theta$  is tuned correctly, the capture clock will record how far the signal has propagated through the delay elements. The distance that the signal has propagated can be measured as the index in the capture registers where least significant bits generally have their post-transition

value, and most significant bits generally have their pre-transition value. This imprecise definition reflects the metastability around the transition point that can cause multiple bit flips. This metastability could contain useful information and ignoring these flips could reduce the entropy of the side channel. This behavior is shown in Rising/Falling Transition 1 of Figure 2.1.

In this paper, we examine three metrics of propagation:

- First Index: The index of the first bit in Output that is not equal to Output [0]

- Last Index: The index of the last bit in Output that is equal to Output [0]

- *Binary Hamming Distance*: For rising transitions, the binary Hamming distance from 64' h\_0000\_0000\_0000\_0000, and for falling transitions, the binary Hamming distance from 64' h\_ffff\_ffff\_ffff\_ffff.

In Figure 2.1 the *First Index* metric will yield the sequence: 38, 20, 36, 19. *Last Index* will yield the sequence: 38, 23, 39, 23. *Binary Hamming Distance* will yield the sequence: 39, 22, 38, 22.

The *First Index* and *Last Index* metric work well if there is a single transition, or if bits in the metastable region are not correlated with PDN variations, and the inter-CARRY primitive delay is small. In contrast, the *Binary Hamming Distance* metric counts multiple transitions and can increase side channel information if the metastability is correlated with PDN variations. In the following chapter we show that the *Binary Hamming Distance* metric optimizes the channel information because there is frequently more than one apparent transition in a sample and inter-primitive timing delay is not linear.

## 2.3 Acknowledgements

Thanks to Dr. Dustin Richmond of the University of Washington and Professor Ryan Kastner of the University of California, San Diego, for the assistance in drafting this chapter. A particular thanks to Dr. Dustin Richmond for the original design of this sensor, and the hands on contributions in this writing. Many of these ideas would not have been possible without the excellent advice and wealth of knowledge from Bill Hunter of the Georgia Tech Research Institute, as well as valuable contributions from Christopher McCarty of the Georgia Tech Research Institute.

# Chapter 3

## **Power Side-channels**

In this chapter we study the use of the Tunable Dual-Polarity TDC for power side-channel attackers in multi-tenant FPGA platforms. We begin with a discussion of the power network of the FPGA and how this can act as a side-channel. Then, we introduce the multi-tenant threat model. We demonstrate that parameter selection, dynamic tuning, and noise reduction is essential for mitigating non-linear behaviors within TDC sensors, extracting information about a co-tenant computation, and improving cross-board generalization. We measure the impact of these techniques in a multi-tenant scenario where the attacker aims to determine the type of computation and microarchitectural implementation of a co-tenant, as well as a Correlation Power Analysis attack on an AES encryption core.

### **3.1 Power Distribution Network**

A power distribution network (PDN) aims to provide a constant voltage to the components of a computing system. A typical power distribution network consists of a switching voltage regulator that supplies a set of target voltages to the on-board system components. Power is provided via printed circuit board wires to the pins of each component. The pins are connected to the on-chip power grid, and provide power to the individual transistors of the system. The voltage regulator of the power distribution network is designed to provide a target voltage within a design margin. With a constant current load, the output voltage of the regulator oscillates between high and low values that are specific to the characteristics of the device as internal capacitance is recharged and discharged. As the current load in the system increases, the frequency of the oscillations increase. Computations in a system consume power, increase the current load, and cause the voltage oscillations to change frequencies. The voltage fluctuations caused by an application running on a system can be measured, characterized, and exploited to undermine the security of the system [ZS18, SGMT18a].

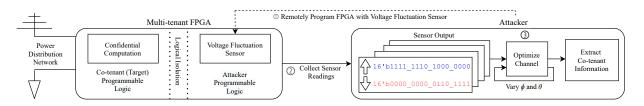

**Figure 3.1**: Remote TDC Threat Model – Step ①: An attacker is given access to a remote multi-tenant FPGA and programs it with a voltage fluctuation sensor. Step ②: The sensor readings are gathered and sent to the attacker for analysis. Step ③: The attacker optimizes the channel capacity by tuning the parameters  $\theta$  and  $\phi$ . When the channel is maximized, the attacker can better extract co-tenant information, such as a cryptography key or implementation detail.

## **3.2** Threat Model

Figure 3.1 describes the proposed threat model. The attacker is provided access to a multi-tenant FPGA and co-locates with a victim tenant. The attack can be performed completely remotely; it does not require physical access to the FPGA or prior knowledge of the system. The attacker has a design with a voltage fluctuation sensor and deploys it on the multi-tenant FPGA. We assume the system provides logical separation of the tenants [HBW<sup>+</sup>07, MM07] and the attacker is restricted to system defined interfaces, e.g., those provided by a shell. The attacker gathers the sensor readings and classifies them to determine a characteristic of the co-located computation.

The attacker is a malicious adversary that aims to extract information about the computations of other tenants utilizing the same FPGA. This could be as simple as whether another tenant is currently using the FPGA (e.g., to know when to launch a fault attack [GOT17, KGT18, SSN<sup>+</sup>19]). The attacker could classify whether a specific type of computation is occurring on the shared FPGA (e.g., is the co-tenant performing encryption?). Going even further, it could infer details about the co-tenant's design (e.g., are they using a soft processor? Is it a RISC-V processor?). The attacker could also learn information about the data being computed upon, e.g., extracting a cryptographic key [ZS18, SGMT18a, GCRS20], and leverage the architectural details learned about implementation and computation duration to increase recovery speeds.

The attacker is given an area of the programmable logic and can implement a voltage fluctuation sensor. Our voltage fluctuation sensor is a variant of a time to digital (TDC) sensor [ZSZF13]. We assume that our sensor will pass any bitstream analysis techniques put in place to detect potential remote attacks [KGT19]. Our sensor passes the checks performed by Amazon as discussed later. Our sensor does not have timing path violations or combinational cycles and thus it is significantly less likely to be detected during bitstream analysis compared to ring oscillator-based sensors.

We do not make any assumptions about where the sensor is placed, e.g., the victim computation does not need to have one of its wires running through it [PHT19, GRE18, RPD<sup>+</sup>18]. However, the sensors are more sensitive to computations that are spatially closer [PHT19, KGT20], and thus, the proximity of the target computation will effect our ability to classify information. Increased physical distances reduce the signal to noise ratio making proper sensor tuning more important in order to extract better information.

Our experiments only consider attacks on computation co-located on the same programmable logic. However, we note that similar attacks have been shown from the FPGA to a CPU on the same die [ZS18], across dies on a 2.5D integrated package [GRS19], and across chips on the same board [SGMT18b, GRS20]. In this section we report results on the impact of  $\theta$ ,  $\phi$ , and propagation metrics on measurements of the Tunable Dual-Polarity TDC and their impact on classifying 13 co-located application circuits.

## 3.3 Experimental Setup

Our experimental platforms are Amazon Web Services (AWS) EC2 F1 instances with Xilinx UltraScale+ XCVU9P-FLGB2104 FPGAs, and six PYNQ-Z2 boards with Xilinx ZYNQ XC7Z020-1CLG400C FPGAs. On the PYNQ systems the device is programmed with our sensor and test designs through the Python Productivity for Zynq (PYNQ) infrastructure. The AWS EC2 F1 instances are launched through the EC2 interface and programmed with the unique AGFI identifier associated with our sensor designs. The AGFI is generated by Amazon's unmodified compilation flow with the design checkpoint we provide. Our sensor has passed all design analysis techniques performed by AWS.

A 64-bit Tunable Dual-Polarity TDC is instantiated on PYNQ-Z2, and a 256-bit Tunable Dual-Polarity TDC on AWS. The launch and capture clock domains operate at 100 MHz. This results in a sampling rate,  $F_{sample}$ , of 25 MHz. MMCM (1), which allows for the phase shifting of  $F_{sample}$ , produces a 100MHz output clock. The internal  $F_{vco}$  is maximized for the two MMCMs so that the step granularity of  $\theta$  and  $\phi$  is maximized with a step size of 11.16 ps on AWS and 14.88 ps on PYNQ.

## 3.4 Applications

Our experiments use our Tunable Dual-Polarity TDC to classify the characteristics of a cotenant. We have 13 unique applications containing of mix of IP cores using different architectural features. The application IP core and the sensor are implemented on the same FPGA. They are logically and physically isolated. The characteristics of the applications are described in the following paragraphs.

**Sensor Only** The primary goal of the sensor only design is to model the lack of another cotenant. This design only contains the voltage fluctuation sensor and associated data collection logic. This mimics a scenario where only the attacker is present on the FPGA.

**Ring Oscillators:** Ring Oscillators are a malicious circuit with the sole purpose of aggressively consuming power. These are implemented as banks of combinational loops, where output value is inverted as the input of the loop. This results in rapid switching and power consumption as the circuit is unable to settle on a single output value. Such a circuit can cause voltage disruptions in the power distribution network and can be used as a covert channel or to induce faults [GOT17, KGT18, SSN<sup>+</sup>19]. Classifying these circuits is important for detecting and removing these malicious circuits from multi-tenant and even single-tenant systems.

**Arithmetic-Heavy:** FPGAs are particularly well suited for high intensity signal processing tasks with arrays digital signal processors (DSPs). We implement, as an approximation of these structures, arrays of DSPs performing a pipelined fused multiply-add operation. All DSPs operate in a single clock domain and compute on data generated by a per-instance, randomly-seeded, linear-feedback shift register.

**Cryptographic Cores:** We study ten different implementations of cryptographic computations. We study two algorithms (AES, PRESENT) implemented on five different architectures (Custom HLS IP core and as software running on Orca, MicroBlaze, PicoRV, and ARM CortexM3 soft processors). This adds ten unique applications: Orca-AES, Orca-PRESENT, MicroBlaze-AES, MicroBlaze-PRESENT, PicoRV-AES, PicoRV-PRESENT, Cortex-AES, Cortex-PRESENT, HLS-AES, and HLS-PRESENT.

### **3.5** θ Tuning and Metric Selection

As shown in Figure 2.2,  $\theta$  is the phase difference between the launch and capture clocks and dictates how long a transition is allowed to propagate through the delay line. It plays two important roles: first,  $\theta$  determines the position of the transition location in the output and can be used to avoid undesirable behavior caused by discontinuities in the FPGA architecture; second,  $\theta$ defines the duration of the sampling window, the time during which the delay line is measuring variations in the PDN and must be long enough to capture variations in the PDN.

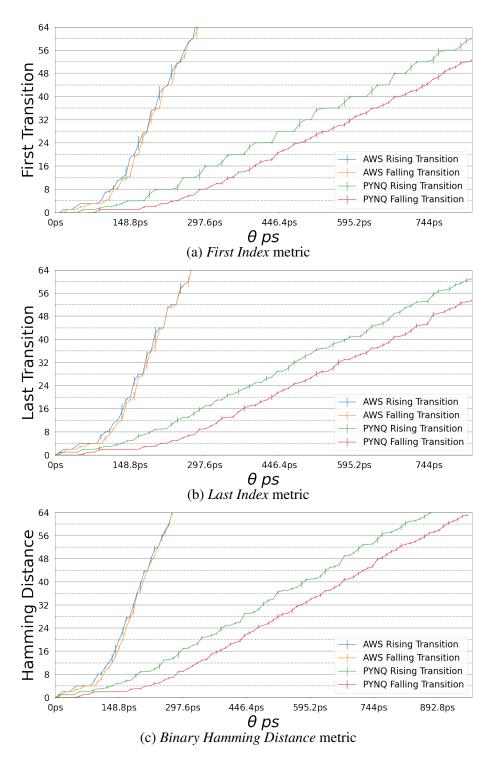

Figure 3.2 demonstrates the effect varying  $\theta$  has on the transition index as measured by the *First Index*, *Last Index*, and *Binary Hamming Distance* metrics across both falling and rising transition polarities. These experiments are performed on the *PYNQ-Z2 Sensor Only* and *AWS Sensor Only* designs. In the experiment  $\theta$  is increased from 0 ps with a step size of 11.16 ps on AWS and 14.88 ps on PYNQ, as determined by the maximum  $F_{vco}$  frequency for the family and device speed grade. At each value of  $\theta$  a trace of 2<sup>14</sup> samples is captured, where a sample is one rising and one falling transition. This process is repeated until the transition index exceeds 64 bits, the maximum length of the delay line for our PYNQ-Z2 implementation. Next, we calculate the transition index using *First Index*, *Last Index*, and *Binary Hamming Distance* metrics, for each value of  $\theta$ , for each trace, for both rising and falling transition polarities. The average value of the trace at each value of  $\theta$  is plotted. Expressed as the error bar at each point is the standard deviation of the respective trace. Standard deviation, as we will show, is a good measure of the sensitivity of the sensor to voltage changes. The rising and falling transition polarities are shown in blue/orange for AWS and red/green for PYNQ. The three sub-graphs correspond to the three propagation metrics from Section 2.2.5.

**Figure 3.2**: Comparison of the three propagation metrics described in Section 2.2 and two transition polarities as  $\theta$  is increased from 0 ps. Vertical lines record the variance of a trace at each value of  $\theta$ . The *First Index* metric is particularly susceptible to plateaus caused by the underlying CARRY4 (7-Series) and CARRY8 (UltraScale+) primitives that cause areas of low sensitivity but has high variance elsewhere. Plateaus indicate regions of low sensitivity. In addition, falling transitions have fewer plateaus and less variance than their rising transition counterparts.

#### 3.5.1 First Index

Figure 3.2a demonstrates the behavior of the rising and falling transitions as measured by the *First Index* metric on both PYNQ-Z2 and AWS. Irregularities in the propagation of the rising transition are immediately apparent within both architectures. Plateaus, regions where the transition index does not increase, appear for ~40 ps on Zynq and ~5 ps on AWS/UltraScale+. The plateaus are interleaved with sloped regions where we see propagation is significantly faster on the UltraScale+ part (~.5 $\frac{bits}{ps}$ ) than on Zynq (~.15 $\frac{bits}{ps}$ ). The sloped regions also reveal the differences in underlying structure: the sloped regions span four bits on Zynq, reflecting the CARRY4 primitives, and span eight bits on AWS/UltraScale+, reflecting the CARRY8 primitives. These sloped regions show the greatest standard deviation at each point, in contrast to the plateaus which show little to none.

Between the rising and falling transitions, the falling transition does not produce such pronounced plateau/slope artifacts. Its overall propagation is more consistent with fewer and less significant plateaus compared to the rising transition. In addition there are fewer points with zero standard deviations.

#### 3.5.2 Last Index

Figure 3.2b demonstrates the behavior of the rising and falling transitions as measured by the *Last Index* metric on both PYNQ-Z2 and AWS. As demonstrated, plateaus are still present but they are less prominent and the standard deviation is more consistent across values of  $\theta$  on the line. Noticeable plateaus still exist where the rising transition resembles that of the *First Index*. Notably, plateaus still present on the UltraScale+ device and demonstrate the same span of eight bits caused by the CARRY8 primitives.

As with the *First Index* metric, between the rising and the falling transition, the falling transition demonstrates fewer plateaus and more consistent standard deviation at each point. The

difference between the rising and falling transitions is significantly less with the Last Index metric.

#### **3.5.3** Binary Hamming Distance

Figure 3.2c demonstrates the behavior of the rising and falling transitions as measured by the *Binary Hamming Distance* metric on both PYNQ-Z2 and AWS. While the *First Index* captures the first point, and the *Last Index* captures the last point the transition has reached, neither fully accounts for metastability within a window. For example, if a rising transition falls within Output [36:40] as in Figure 2.1, neither metric is able to discern between 4b' 0101 and 4b' 0111. Multiple transitions could encode important information about the state of the PDN and reduce the effect of architectural discontinuities. The *Binary Hamming Distance* metric described in Section 2.2.5 does not suffer from this limitation.

The data in Figure 3.2c demonstrates that there are few plateaus when using the *Binary Hamming Distance* metric, and that the standard deviation is relatively consistent across the delay line. As the case in the previous two metrics, the falling transition is less affected by CARRY primitive boundaries and has a more consistent standard deviation across all points. However, the maximum standard deviation is less than that of the first index metric.

#### 3.5.4 Analysis

A careful choice in metric of propagation and transition polarity is clearly important because it can affect the sensitivity and range of the sensor. Circuits can cause characteristic amounts of PDN variation, and some circuits may cause small variations and some circuits may cause large variations. The variable  $\theta$  does provide the ability to choose where in the delay line the transition falls, and therefore the ability to avoid plateaus, but the range can be limited by the underlying carry primitives. For example, if *First Index* and positive transition polarity is chosen as a metric of propagation, it is possible to tune  $\theta$  such that the transition avoids plateaus and lands in a region with high standard deviation. This may be extremely sensitive, but this offers at most 4 bits of swing on Zynq and 8 bits of swing on UltraScale+. Outside of those regions disruptions in the PDN may be lost in the surrounding plateaus. A consistent slope and variance at each point is desirable because it leads to high sensitivity and predictable response in the presence of large and small PDN variations. This is useful in our attack scenario where we are trying to determine the type of core and assume nothing about the variations on the PDN.

For the remainder of the paper we use the *Binary Hamming Distance* metric for measuring rising and falling polarities. This selection reduces the number of plateaus in comparison to the other combinations (*First Index* rising, *First Index* falling, *Last Index* rising, *Last Index* falling). It also provides consistent standard deviation compared with these combinations, which demonstrates sensitivity at each point.

## **3.6** • Tuning and Background Subtraction

$\phi$  is the phase relationship between the target clock and the launch clock of the sensor. Our Tunable Dual-Polarity TDC can dynamically adjust  $\phi$  to tune to the target clock and maximize measured information. This provides the ability to reliably isolate where information channel is maximized between the co-tenant application and sensor. We find that this has significant impact on the side-channel information recovery of the sensor.

To demonstrate this, we sweep  $\phi$  through two complete phase rotations (4 $\pi$ ). For  $F_{sample}$  equal to 25 MHz this corresponds to 80ns. This process is performed twice: once as a measure of the background environment when the computation is disabled, and again when a co-tenant has been enabled. At each position of  $\phi$ , two traces of 1024 samples are captured. One trace records the rising transition polarity ( $\uparrow$ ) where  $\theta$  maximizes the rising transition standard deviation samples and the other trace records the falling transition polarity ( $\downarrow$ ) where  $\theta$  maximizes the falling transition standard deviation for the background environment is computed for the falling transition standard deviation for the background environment when the computation is disabled, and again when a co-tenant has been enabled. At each position of  $\phi$ , two traces of 1024 samples are captured. One trace records the rising transition standard deviation samples the rising transition standard deviation for the background environment when the falling transition polarity ( $\downarrow$ ) where  $\theta$  maximizes the falling transition standard deviation samples. The *Binary Hamming Distance* is computed for

each of these transition types. The average ( $\mu$ ) as well as standard deviation ( $\sigma$ ) of each trace is calculated.

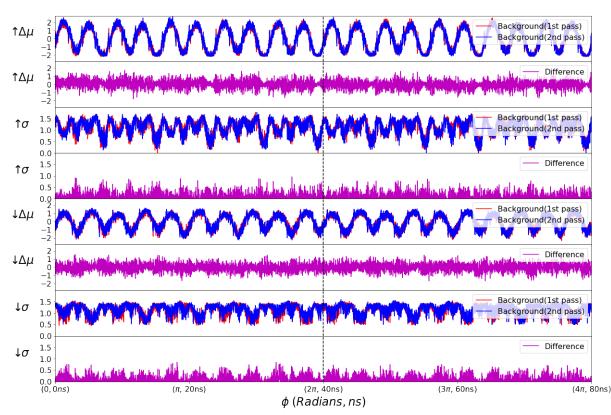

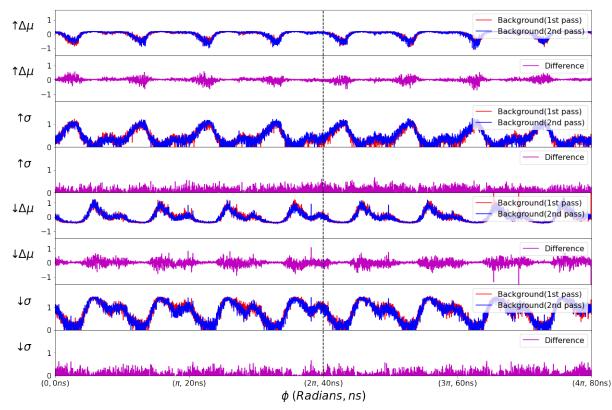

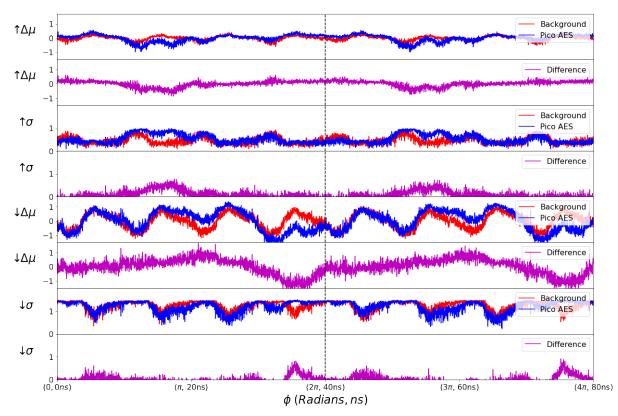

Figures 3.3, 3.5, and 3.4 demonstrate the result of sweeping  $\phi$  over the range of  $4\pi$  on three different designs: *AWS Sensor Only*, *PYNQ-Z2 Sensor Only* and *PYNQ-Z2 PicoRV AES*. The first and fifth row in each subfigure plot the zero-centered trace average for the rising transition ( $\uparrow \Delta \mu$ ) and falling transition ( $\downarrow \Delta \mu$ ). The raw offset in the *Binary Hamming Distance* is unimportant, so we consider the deviations from the average across all values of  $\phi$ . The blue line is the data recorded when the computation is off (Background), and the red line is the data recorded when the target was on (if applicable). The second and the sixth row plot the point-wise difference between the red and the blue line in their respective preceding plots. The third and the seventh row in each subfigure plot the trace *Binary Hamming Distance* standard deviation ( $\sigma$ ) for the rising transition ( $\uparrow \sigma$ ) and falling transition ( $\downarrow \sigma$ ).

The fourth and the eighth row plot the point-wise difference between the the red and the blue line in their respective preceding plots.

#### 3.6.1 AWS Sensor Only

Figure 3.3 shows the behavior of the Sensor Only design on the AWS platform. The Background sweep is performed to record the environment. A second background sweep is then performed to determine whether background is consistent across multiple sweeps of  $\phi$ . A clear signal emerges in the *Binary Hamming Distance* of both edges on both background sweeps (rows 1 and 5,  $\uparrow \Delta \mu$  and  $\downarrow \Delta \mu$ ). When the difference of the two  $\phi$  sweeps is taken, the *Binary Hamming Distance* ( $\uparrow \Delta \mu$  and  $\downarrow \Delta \mu$ ) as well as the standard deviation ( $\uparrow \sigma$  and  $\downarrow \sigma$ ), is reduced to a flat line.

The results demonstrate that there is significant background noise that has an effect on both the *Binary Hamming Distance* as well as the standard deviation of a trace. 20 peaks of equal amplitude appear over a range of 80 ns within the *Binary Hamming Distance*, which implies the existence of 250 MHz logic on the FPGA. This may be the internal logic of the sensor, which

**Figure 3.3**: Measuring sensor output as  $\phi$  is swept from 0 to  $4\pi$  on the AWS Sensor Only Design. Background noise is consistent across multiple sweeps of  $\phi$ .

runs at 100 MHz, but it is likely the AWS shell logic which runs at 250 MHz. This is consistent across multiple sweeps of  $\phi$ . Using background subtraction techniques [Pic04] it can be removed to isolate the target.

### 3.6.2 PYNQ-Z2 Sensor Only

Figure 3.4 demonstrates the same experiment performed on the PYNQ-Z2 platform. Rather than 250 MHz, we now observe background peaks that indicate 100 MHz synchronous logic. As on AWS, this information is consistent across multiple sweeps, and when the background is subtracted, all variation in the *Binary Hamming Distance* as well as the standard deviation is reduced to flat line, with little noise.

**Figure 3.4**: Measuring sensor output as  $\phi$  is swept from 0 to  $4\pi$  on the PYNQ-Z2 Sensor Only Design. Background noise is consistent across multiple sweeps of  $\phi$ .

## 3.6.3 PYNQ-Z2 PicoRV AES

Figure 3.5 demonstrates the same experiment performed on PYNQ-Z2 platform when the PicoRV AES design is operating at 25 MHz. In contrast to the previous two experiments, we take a single background sweep of  $\phi$  with the PicoRV core deactivated, then another sweep of  $\phi$  with the processor activated. There appear subtle differences in the *Binary Hamming Distance* as well as standard deviation between the background  $\phi$  sweep and the PicoRV-AES  $\phi$  sweep.

Background subtraction produces a single distinct peak over a range of  $2\pi$  in the *Binary Hamming Distance* ( $\Delta\mu$ ) and standard deviation ( $\sigma$ ) plots. We attribute this single peak to the PicoRV AES core running at 25 MHz. This behavior is consistent across designs, algorithms, and architectures. This position of  $\phi$  represents not just where standard deviation is maximized (which may be muddied by the presence of background information), but where the channel contains

**Figure 3.5**: Measuring sensor output as  $\phi$  is swept from 0 to  $4\pi$  on PYNQ-Z2 PicoRV AES design. Background subtraction is necessary to isolate a target from other information sources on the system and reveal the value of  $\phi$  where the side channel between the target and the sensor is maximized.

maximum information about the co-tenant. We show in Section 3.6.4 that this is the best location for tuning the sensor and recovering side-channel information.

### 3.6.4 Effects of Tuning on Classification

As a practical measure of the benefits of tuning, we demonstrate an attack where we accurately classify a co-tenant computation in a multi-tenant system. As described in Section 3.2, an attacker uploads a voltage fluctuation sensor to a remote multi-tenant FPGA environment with the intention of extracting the architecture and algorithm of co-tenant computation. Such an attack serves as a fundamental violation of the application anonymity guaranteed by such a multi-tenant system. The attack is performed on each of the 13 applications on 5 PYNQ-Z2

(c)  $(\downarrow \theta_{max}, \phi_{back})$

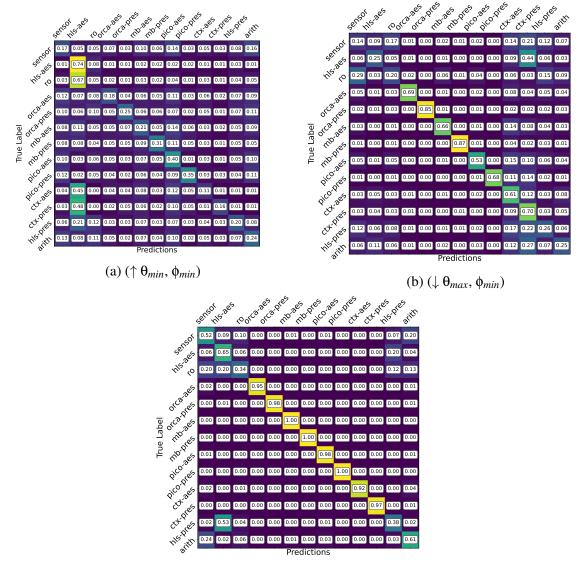

**Figure 3.6**: Our Tunable Dual-Polarity TDC is employed in a 13-way classification task where an attacker extracts the type of co-located computation. The ability to distinguish co-tenant computations is a measure of side-channel information contained in the sensor's traces. The computations are introduced in Section 3.4. 3.6a represents the worst-case where a TDC cannot reconfigure  $\phi$  and  $\theta$  and achieves 32% accuracy. In 3.6b the TDC can tune  $\theta$  and improves to 51% accuracy. In 3.6c both  $\theta$  and  $\phi$  have been tuned and background subtraction is applied to isolate co-tenant information to achieve 75% accuracy.

platforms as follows.

$\theta$  **Tuning** In the following experiment we consider four configurations of  $\theta$ : the position where standard deviation has been maximized for a particular rising falling transition polarity ( $\uparrow \theta_{max}$

and  $\downarrow \theta_{max}$ ), and where standard deviation has been minimized for a particular rising falling transition polarity ( $\uparrow \theta_{min}$  and  $\downarrow \theta_{min}$ ). We perform a sweep through the 64 bit delay line and record the average and standard deviation of a trace at each point. The point at which standard deviation is maximized (minimized) in the rising transition we label  $\uparrow \theta_{max}$  ( $\uparrow \theta_{min}$ ) and similarly  $\downarrow \theta_{max}$  ( $\downarrow \theta_{min}$ ) for the falling transition.

$\phi$  **Tuning** The sensor's  $\phi$  will be configured three ways: first at a state of absolute maximum standard deviation ( $\phi_{max}$ ), at its absolute minimum standard deviation ( $\phi_{min}$ ), and finally the maximum standard deviation under the background subtraction ( $\phi_{back}$ ) process of Section 3.6. Just as in Section 3.6,  $\phi$  is shifted in 14.88 ps increments 2688 times at each point capturing a trace of 128 samples—once to capture background noise ( $\sigma_{back}$ ), and again once the target application has been enabled ( $\sigma_{active}$ ). In the tuning process,  $\phi_{max}$  ( $\phi_{min}$ ) is the maximum (minimum) standard deviation of the  $\sigma_{active}$  sweep for a given transition type. The position of maximum standard deviation of  $\sigma_{active} - \sigma_{back}$ .

**Data Collection** First, the target design and sensor are loaded onto the device, and  $\theta$  is positioned at one of ( $\uparrow \theta_{max}, \downarrow \theta_{max}, \uparrow \theta_{min}$ , or  $\downarrow \theta_{min}$ ). Second,  $\phi$  is configured to one of ( $\phi_{max}, \phi_{min}, \phi_{back}$ ). We examine the following tuning combinations of ( $\theta, \phi$ ):

- 1. ( $\uparrow \theta_{min}, \phi_{min}$ ): This emulates the worst-case of a non-tunable TDC. In a non-tunable TDC attack scenario  $\phi$  is random at initialization. Because  $\phi$  may be positioned anywhere on the spectrum 0 to  $2\pi$ , we pick the case when standard deviation is minimized for the rising transition. Depending on the static load on the PDN, a poor  $\theta$  may cause the transition to fall on a plateau. This serves as a baseline to show how information recovery can be improved with proper tuning.

- 2. ( $\downarrow \theta_{max}, \phi_{min}$ ): This introduces  $\theta$  tuning to demonstrate how it improves the ability of the sensor to resolve co-tenant information.

- 3. ( $\downarrow \theta_{max}, \phi_{max}$ ): This dataset demonstrates significance of  $\phi$  tuning on classification accuracy.

- 4. ( $\downarrow \theta_{max}, \phi_{back}$ ): This dataset demonstrates how background subtraction improves our ability to optimize the co-tenant side-channel.

- 5. ( $\uparrow \theta_{max}, \phi_{back}$ ): To determine which transition polarity captures the most information, we generate a data set to compare against ( $\downarrow \theta_{max}, \phi_{back}$ ).

After the sensor is configured, the given computation is launched and a trace of  $2^{16}$  samples is gathered. This process is performed 100 times on each application for a total of 1300 traces per tuning combination per board.

**Post-processing** For a group of 1300 traces from a single tuning configuration ( $\theta$ ,  $\phi$ ) on a single board, we randomly segment each trace into 10 sub-traces of 2<sup>13</sup> samples. Each sub-trace is de-trended to remove the DC offset. The Fourier transform of the processed trace is then computed. From an original set of 1300 traces we are left with 1000 rising transition Fourier transforms and 1000 falling transition Fourier transforms for each application, amounting to 26000 Fourier transforms overall per board per configuration.

**Network Architecture** We train a simple neural network of only one fully connected layer. To model an attack scenario where training data is gathered on a different board than where the attack is performed we perform cross-validation with 5 different training scenarios. Each scenario has a different set of 4 training boards and a 5th testing board. We report the average of the classification accuracy and the cross-entropy loss. The classification accuracy is a measure of how accurately our network can classify among the 13 classes of computation. Cross-entropy loss indicates how well our network generalizes to unseen data, as it measures how far away the model's predictions are from the true labels. A perfect model would have a loss of 0.

#### **Classification Results**

The results of our experiments are shown in Table 3.1, and select confusion matrices from our 13-way experiment are shown in Figure 3.6. The results are summarized below:

| Tuning                                   | Accuracy (%) | Loss  |

|------------------------------------------|--------------|-------|

| $(\uparrow \theta_{min}, \phi_{min})$    | 32.146       | 2.159 |

| $(\downarrow \theta_{max}, \phi_{min})$  | 51.160       | 1.644 |

| $(\downarrow \theta_{max}, \phi_{max})$  | 75.788       | 0.834 |

| $(\downarrow \theta_{max}, \phi_{back})$ | 75.552       | 0.733 |

| $(\uparrow \theta_{max}, \phi_{back})$   | 80.943       | 0.668 |

Table 3.1: Average accuracy and loss across configurations.

( $\uparrow \theta_{min}, \phi_{min}$ ): The baseline dataset exhibits predictably poor performance in our classification task as shown in Table 3.1 with only 32% accuracy. This configuration results in a poor classifier which is unable to accurately determine the co-tenant application. The confusion matrix in Figure 3.6a demonstrate that the classifier struggles across all applications and is not resolving information about any one of the co-tenant designs. A TDC which is unable to tune  $\phi$  and  $\theta$  can expect this performance as a lower bound.

$(\downarrow \theta_{max}, \phi_{min})$ : With the introduction of  $\theta$  tuned to a maximum position we see an immediate improvement in classification accuracy from 32% to 51% in Table 3.1. This shows that with the introduction of proper  $\theta$  tuning to avoid plateaus, measured information increases. The confusion matrix for this dataset is shown in Figure 3.6b. It demonstrates that the classifier is beginning to distinguish between soft-processors and the applications that run on them, but fails in all other cases.

$(\downarrow \theta_{max}, \phi_{max})$ : With the introduction of  $\phi$  tuning, accuracy improves to 75% in Table 3.1. The confusion matrix for this data set is shown in Figure 3.6c. This is a robust classifier for determining the co-tenant application.

$(\downarrow \theta_{max}, \phi_{back})$ : To evaluate the effects of background subtraction, we report our network's average accuracy and loss for  $(\downarrow \theta_{max}, \phi_{max})$  and  $(\downarrow \theta_{max}, \phi_{back})$ . As seen in Table 3.1, the network actually performs 0.236% better without background subtraction; however, with background subtraction, the network's loss is lower (0.733 vs 0.834 loss). This indicates that with background subtraction our network generalizes better.

To investigate this result and understand how well the network generalizes to boards on which it has not trained, we expand on our cross-validation setup. We train on an increasing number of boards, starting with training on 1 board and testing on the 2nd and increasing until we train on 4 boards and test on a 5th. Similar to our previous cross-validation testing, we create training setups that involve all possible combinations of training on *n* boards and testing on the n + 1st. If we want to choose *n* boards for training, then there are  $\binom{5}{n} * (5 - n)$  ways to split the 5 boards into a training scenario with *n* training boards and a separate testing board. Training is then performed on  $(\downarrow \theta_{max}, \phi_{max})$  and  $(\downarrow \theta_{max}, \phi_{back})$  datasets. By training on an increasing number of boards, we gain insight on how well our network generalizes to unseen boards given the number of boards it learned from during training. We call this cross-board generalization.

We report the results of our cross-board generalization experiment in Figure 3.7. As the number of training boards increase, the median accuracy increases and the median loss decreases. This is expected: When the network has data from more boards, it learns more about the computations being performed on the board rather than the idiosyncrasies shared by the training boards. When training and testing on the same board the network has very high accuracy (nearly 100%) and very low loss (nearly 0). We expect this behavior because, with data from only one board, the network does not generalize to aspects of the computation, but rather artifacts of the data set. When we train on 1 board and test on a 2nd, this unfair advantage is removed and accuracy plummets. Figure 3.7 clearly shows a drop in accuracy and an increase in loss. As we train on more boards, the accuracy then subsequently increases and the loss decreases as the

**Figure 3.7**: Training on an increasing number of boards with background subtraction ( $\downarrow \theta_{max}$ ,  $\phi_{back}$ ) and without ( $\downarrow \theta_{max}, \phi_{max}$ ). Testing always occurs on a board separate from the training set, except for when we train and test on the same board, which we denote in the x-axis as "S".

idiosyncrasies are ignored.

The distributions of accuracy and loss as we train on more boards behave differently when the network trains on data with background subtraction versus data without background subtraction. As seen in Figure 3.7b, the interquartile range (IQR) decreases when background subtraction is added. When we train on 4 boards and test on a 5th, the IQR without background subtraction is 0.429, whereas the IQR with background subtraction is 0.074, an improvement of  $5.8 \times$ . With a smaller distribution, the network is more likely to generalize to unseen boards. This is also reflected in the distribution of the accuracy in Figure 3.7a. In the same 4 training board setup, the IQR of the accuracy with background subtraction is  $2.3 \times$  smaller than without

background subtraction.

( $\uparrow \theta_{max}, \phi_{back}$ ): The use of the rising transition increases the accuracy from 75% to 80% and decreases the loss from .733 to .626. This indicates that the rising and falling transitions contain different information, and that both transitions, when properly tuned, perform well in this classification task.

**Figure 3.8**: Evaluating performance of the CPA attack for configurations obtained via the  $(\uparrow \theta_{max}, \phi_{back})$  and  $(\uparrow \theta_{min}, \phi_{min})$  tuning methods. Lower average PGE indicates that the attack is performing better, as the correct subkey values are ranked as more likely after processing fewer traces.

# **3.7 Effects of Tuning on CPA**

If an attacker has used the network to identify the presence of a AES core, they may begin a key extraction through a Correlation Power Analysis (CPA) attack [BCO04]. To evaluate the benefits of tuning, we perform this attack using different sensor configurations. CPA attacks can be used to recover a cryptographic key from voltage fluctuation traces taken while the victim is performing multiple AES encryption operations. As previously observed [SGMT18a], voltage fluctuations detected by TDCs depend on the the value of the secret key, so measuring the voltage fluctuations enables an attacker to infer information about the key. In a CPA attack, the collected traces are first aligned so that a particular moment of the AES encryption computation appears at the same offset of all time-series trace data. Next, a leakage model is used to hypothesize how the voltage fluctuations should vary with different guesses for the unknown key bytes. If the hypothesized fluctuations correlate with the measured fluctuations, the guessed key bytes are likely correct. In practice, the traces are noisy, so it takes several thousand traces for the computed correlation of the correct hypothesis to be clearly larger than the computed correlation of the incorrect hypotheses. The greater the signal-to-noise ratio of the ratio of the trace data, the fewer traces are required for successful recovery. In the most basic attack against AES-128, each of the 16 "subkey" bytes in the key are considered independently. With 256 possible values for each subkey, this leads to an efficient key recovery method.